1. LE PRINCIPE DES OPÉRATIONS EN DRAM (dynamic random access memory) fonctionnement physique interne.

1.1 Le constituant de base.

Un réseau de mémoire DRAM peut être vu comme

un tableau carré de cellules. Chaque cellule ou point de mémoire

est constituée d'un condensateur et d'un transistor de commande.

La charge de la capacité représente la valeur du bit; à

charge nulle, le bit vaut 0; à charge pleine pleine, il vaut 1.

Le transistor commande la mise en court circuit du condensateur avec un

fil de colonne pour charger ou décharger ce condensateur selon la

tension addichée sur le fil.

1.2 Lecture et écriture du point de mémoire.

En écriture comme en lecture, les transistors de la

ligne deviennent passants par application de la tension de grille.

En écriture, tous les condensateurs sont au départ

vides ou doivent être vidés par lecture. Une tension est appliquée

sélectivement aux colonnes qui correspondent à un 1. Les

condensateurs correspondants sont chargés.

En lecture, les transistors d'une même ligne laissent

s'écouler les charges emmagasinées dans les condensateurs

vers les fils de colonne attachés. Au bout de chaque colonne, un

amplificateur restitue le signal correspondant et charge la bascule correspondante

d'un registre de ligne.

La ligne lue doit TOUJOURS être récrite dans la mémoire car la lecture a vidé les charges.

Il n'y a donc qu'un seul CYCLE d'écriture comme de lecture qui est composé :

1.3 Rafraîchissement.

Les capacités ne gardent pas leur charge indéfiniment

en raison de courants de fuite à travers le substrat. Il faut les

recharger périodiquement par l'opération nommée rafraîchissement

à faire périodiquement entre 4 et 16 ms). Cette opération

est une lecture systématique de chaque ligne suivie de la réécriture.

Un contrôleur de rafraîchissement détermine l'intervalle

de temps maximum entre deux rafraîchissements et un compteur de lignes

désigne périodiquement la ligne à rafraîchir.

Il existe deux grands modes de rafraîchissement:

burst refresh: toutes les lignes de la mémoire sont rafraîchies

consécutivement à chaque période de rafraîchissement.

Toutes les opérations normales de lecture et décriture sont

arrêtées pendant le cycle de rafraîchissement

distributed refresh: chaque ligne est rafraîchie à

intervalles réguliers, entre les opérations normales de lecture

et décriture. Sauf à disposer dans le circuit de ressouces

suoolélentaires, le nombre de lignes est limité par les opérations

de rafraîchissement. Supposons par exemple qu'une mémoire

ait 1024 lignes et une périodicité de rafraîchissement

de 8 ms, une ligne decrait être rafraîchie toutes les 8ms/1024

= 7.8 µs ce qui n'est pas possible eu égard au temps nécessaire

pour l'opération.

|

|

|

|

2. FONCTIONNEMENT GLOBAL

2.1 Temps significatifs.

Sa durée totale est le TEMPS DE CYCLE. Cette notion

est interne à la mémoire, elle est vue comme un tout par

le processeur.

Les autres temps ont des définitions mal fixées.

TEMPS D'ACCÈS, durée entre l'adresse en position

sur le bus et la fourniture de la donnée sur le bus.

TEMPS DE LATENCE, délai entre la demande du processeur

et l'entrée dans le décodeur d'adresse, il contient la mise

en position sur le bus d'adresse et le passage dans le contrôleur

de la mémoire. Parfois il inclut la fourniture du premier mot (temps

d'accès)

2.2 Les caractérisations des mémoires DRAM

Elles sont toutes temporelles.

On voit des expressions comme 5-2-2-2 ou 3-1-1-1 etc. Il s'agit

de nombres de cycles du bus supposé connu. Le premier est le délai

d'obtention du premier mot, les autres des trois mots suivants. Cette habitude

a été prise quand les mémoires étaient organisées

en octets et que le mot était de 32 bits. Il fallait 4 lectures

pour former un mot. On a conservé cette expression.

On utilise aussi le débit en Mo/s et le temps d'accès,

couramment 50, 60 ou 70 ns.

Le temps de cycle n'est jamais présenté.

NOTE 1 Une habitude détestable a été

prise de caractériser les mémoires non pas par leur débit

mais par une fréquence. La compréhension n'en est pas facilitée.

NOTE 2 Les indications de fréquence

et de débits sont toujours données dans le cas le plus favorable.

Par exemple :

Sur un bus cadencé à 66 MHz, une mémoire EDO

donnée pour 5-2-2-2, c'est à dire 5 cycles pour la première

donnée, 2 cycles pour chacune des trois suivantes, sera une mémoire

à 33 MHz ! On ne tient compte que des accès de valeur 2.

Si la même fournit des mots de 32 bits, on dira que c'est une mémoire

à 132 Mo/s. La première donnée est comptée

pour rien ainsi que le temps d'indisponibilité qui suit les quatre

lectures. Les indications de performances sont de la même veine que

les annonces publicitaires d'assurances d'hospitalisation : jusqu'à

1000 F/jour, à partir de 200 F/mois. (pour 200F/mois, vous recevriez

300 F/jour, il faudrait cotiser à 600 F/mois pour avoir 1000 F/jour).

2.3 Enchaînement des opérations pour une lecture en SDRAM

Pour réduire le nombre de lignes dadresse, les DRAMs utilisent

un multiplexage de ladresse: les bits dadresse de la ligne et de la colonne

sont envoyés en séquence.

Tout dabord, les bits dadresse de la ligne sont envoyés,

et stockés internement grâce au signal RAS «row address

strobe».

Ensuite, les bits dadresse de la colonne sont envoyés,

identifiés par le signal CAS «column address strobe».

L'adressage du tableau est fait via des générateurs d'adresses de ligne RAS pour «row adress selector» et de colonne CAS pour «column adress selector». L'adresse de ligne sélectionne une ligne.

Placement de l'adresse de ligne (RAS) sur les pattes du circuit

1 cycle;

Émission interne de l'adresse de ligne 1 cycle;

Sélection de la ligne à lire dans le tampon de transistors

de détection;

Suppression de l'adresse de ligne;

Affichage de l'adresse de colonne CAS;

Lecture de la ligne de bits dans le tampon de transistors de détection,

2 à 3 cycles;

Extraction-écriture des bonnes colonnes dans le tampon de

sortie en 2 ou 3 cycles, on dispose alors du premier mot en 8 premiers

octets;

Sortie du premier mot vers le bus 1 cycle.

À partir de là :

La mémoire RAM classique récrit la ligne en tant

qu'opération interne.

La mémoire «burst» envoie à raison d'un

mot par cycle les 3 mots suivants.

2.4 Exemple d'informations figurant sur une barrette de mémoire SDRAM PC100, imposé par Intel :

Tout module de mémoire réputé être de la PC100 doit comporté au moins les informations PC X-ABC-DEF :

X Fréquence d'opération

en Mhz pour laquelle le module est réputé travailler. (ex:

66MHz, 100MHz, 125MHz, 133 Mhz)

A Latence CAS minimale

«sdram cycle lenght/sdram

Column

Adress

Select

latency time, en nombre de cycles d'horloge, souvent 2 ou 3 lorsque le

module SDRAM travaille à la fréquence d'horloge X. Une

valeur de 2 donnera une meilleur performance, quoique moins stable si la

mémoire n'est pas certifiée CAS 2.

B Valeur Trcd minimale

ou délai de RAS vers CAS «sdram time RAS-to-CAS

delay»,

en nombre de cycles d'horloge, souvent 2 ou 3 lorsque le module SDRAM travaille

à la fréquence d'horloge X, normalement 2. Utiliser une

valeur plus basse augmente la performance, mais peut créer une instabilité.

C Valeur Trp minimale

ou Précharge RAS «sdram

time

ras

precharge»,

en nombre de cycles d'horloge, souvent 2 ou encore fast est le délai

de pré-chargement de la mémoire lorsque le module SDRAM travaille

à la fréquence d'horloge X.

D Valeur Tac minimale

(time Access from Clock) en ns, souvent 6ns, 6,5ns

ou 7ns, lorsque le module SDRAM travaille à la fréquence

d'horloge X.

E Numéro de révision

SPD

«serial

presence

detect revision number».

Cette information est normalisée mais peut varier avec le temps.

Il certifie que le module possède des données en mémoire

EEPROM intégrée dans la puce conforme à la norme Intel

'Revision #1.2'. Ce champ a un ou deux chiffres.

F Ce champ est réservé,

normalement il contient 0.

Exemple : le module PC100-322-620 indique que la mémoire SDRAM est prévue pour une utilisation à 100MHz, avec une latence CAS à 3, un Trcd à 2, un Trp à 2, un Tac à 6ns, un SPD Rev.à 1.2

Informations relatives au fabricant, figurant sur les barrettes

:

| Fabricant | Préfixes |

| Fujitsu | MB |

| Hitachi | PDC |

| Hyundai | HY |

| IBM | IBM |

| LG Semiconductors | GM |

| Micron | MT |

| Mitsubichi | MSM |

| Mosel Vitelic | V |

| NEC | µPd |

| Oki | MSM |

| Samsung | KM |

| Siemens | HYB |

| Texas instruments | TMS |

| Toshiba | TC |

Actuellement, il n'y a pas de norme établie sur la description de l'arrangement interne des puces de mémoire et leurs performances. Certains fabricants utilisent un code à deux chiffres ou lettres, d'autres utilisent trois ou plus.

3. COMMENT AUGMENTER LES DÉBITS

Les modifications portent sur les moyens internes gestion du circuit.

Ils peuvent être de deux ordres seulement :

.jouer sur synchrone ou asynchrone;

.inventer de nouvelles procédures d'accès.

1) La détermination des instants. Toutes les opérations précédentes étaient faites au rythme propre des éléments du circuit de mémoire. C'était une technique asynchrone. À son avantage, les opérations étaient faites au rythme maximum. À son désavantage, chaque accès doit être accompagné d'un signal strobe qui indique que la valeur (par exemple une adresse) est présente. À l'opposé, on a envisagé un fonctionnement synchrone rythmé par l'horloge présente sur le bus. Le fait que la RAM soit alors prévisible libère des cycles utilisables. Les signaux de disponibilité sont alors inutiles.

2) Le temps d'attente de placement de l'adresse de colonne peut être évité en supprimant le multiplexage.

3) Au lieu de ne lire que les seuls bits utiles et de recharger ensuite la ligne de mémoire, on peut conserver dans un tampon tous les bits de la ligne, en espérant que la règle de localité s'appliquera utilement autant en lecture pour les bits suivants qu'en écriture. On ne rechargera la ligne que si l'on ne peut faire autrement, rafraîchissement ou accès à une autre ligne.

4) On peut augmenter la taille du mot et écrire ses bits sur une même ligne. Au lieu de lire un seul octet par ligne de mémoire, on lira un mot entier, 64 bits par exemple. En contrepartie, il faudra plus de pattes d'entrée-sortie sur la puce.

5) On peut loger dans le circuit plusieurs bancs à accès indépendants. On pourra faire des lectures ou écritures entrelacées sur les bancs.

6) On peut mettre en place plusieurs des moyens précédents simultanément.

Néanmoins, dans tous les cas, on ne pourra pas éviter le temps de lecture de la ligne pour la première opération et ensuite le temps de rechargement.

4. LES SOLUTIONS ASYNCHRONES

Le fonctionnement de principe ci-dessus a été modifié comme dit ci-après par l'invention de variantes.

4.1 Accès en Mode Page (Page mode access)

Cela a été la première évolution marquante par application de la recette numéro 3.

L'unité de lecture est une ligne pour les électroniciens, elle est nommée page par les informaticiens. Que ce soit pour une lecture ou une écriture, elle est lue et placée dans le registre de ligne (ou de page). L'accès en mode page consiste à faire la lecture ultérieure d'autres éléments de la même ligne par l'affichage de CAS seul, sans refaire tout le cycle.

Ce mode page a été rapidement abandonné et

remplacé par le suivant.

4.2 Accès en Mode Page rapide (Fast mode page access, FPM)

C'est le précédent modifié par application partielle de la recette numéro 2.

Au lieu de ménager une attente entre la suppression de l'affichage RAS et le début de l'affichage de CAS, on enchaîne CAS immédiatement. La disponibilité des bits provoquera la suppression de CAS alors qu'avant cela la suppression de CAS était le signal de disponibilité des bits. On n'attendra donc plus un signal préétabli.

Ce mode a été le plus utilisé jusqu'à la fin de l'année 98. Parmi ses avantages, il réduit la consommation de courant qui aurait été nécessaire pour lire et relire la même ligne.

Il est toutefois limité par le fait que l'on doit attendre que les tampons d'entrée et sortie soit alimentés par le bus ou vidés sur lui.

Ce mode est caractérisé par une séquence telle que 6-3-3-3. Elle veut dire que la première donnée sera disponible au bout de 6 cycles de bus, et les suivantes en 3 cycles de bus chacune.

Ce mode est pratiquement abandonné car il est resté cher à cause d'une demande faible et de l'arrivée du suivant.

Ici déjà et dans la suite, le temps d'accès à un bit est différent selon qu'il est le premier ou l'un des suivants. On relie les performances du bus et celles de la mémoire en donnant la liste des quatre temps d'attente de quatre données lues successivement. Les FPM ont 5-3-3-3 soit cinq temps d'attente, suivi par 3 puis 3 puis 3 temps d'attente.

4.3 Accès en mode hyperpage ou Extended data out (HyperPage Mode access ou EDO)

C'est la dernière modification majeure utilisée. Elle consiste à ne plus neutraliser les tampons d'entrée et sortie à l'apparition du CAS, comme on le voit sur le schéma suivant. Le temps de position de CAS est minimum. Le gain est de l'ordre de 40% sans modification externe du circuit ni consommation supplémentaire de transistors. Cette technique est donnée pour bien fonctionner pour des bus jusqu'à 83MHz. Si le circuit fait mieux que 55 ns pour le premier accès, on peut le faire fonctionner avec un bus à 100 MHz. Un autre avantage est que la modification purement interne au circuit ne demande pas de carte mère spéciale à l'opposé des techniques synchrones.

La production est arrêtée depuis 1998, supplantée par les SDRAM.

Pour une machine équipée en EDO il n'y a pas de motif

de passer au SDRAM tant que l'on a un bus limité à 83 MHz.

Le cycle typique d'EDO est 5-2-2-2 à 66 MHz, alors qu'une mémoire

SRAM est en général donnée pour 2/1/1/1.. On l'interprète

comme suit : cinq cycles du bus d'attente pour la première donnée,

2 cycles d'attente pour les trois suivantes de la même ligne. On

ne compte pas le temps de rechargement.

4.4 Burst EDO (BEDO)

Burst EDO a eu une carrière très courte. Il a pratiquement disparu à peine né. Le principe en était la fabrication automatique interne au circuit des trois adresses qui suivaient un accès et non plus leur affichage par CAS. Le cycle était 4-1-1-1. Sa disparition est due au choix d'Intel approuvé par beaucoup de fabricants pour le SDRAM, technique synchrone.

5. LES SOLUTIONS SYNCHRONES

Les avantages principaux des solutions synchrones ont été mentionnés plus haut.

Leur nom commun est SDRAM (synchronous dynamic ram). Elles fonctionnent

toutes sous la forme de 8 puces chacune contenant des octets, leur concaténation

fournit un mot de 64 bits.

Leurs noms propres sont SDRAM II ou DDR

(double-data rate), CDRAM (cache DRAM), DRDRAM (direct

Rambus DRAM), ESDRAM (enhanced SDRAM), JEDEC

SDRAM qui est le standard ordinaire (JEDEC Standard dynamic RAM, SLDRAM

(sync-linc DRAM), DDRDRAM.

Le JEDEC (Joint Electron Device Engineering Council) est l'organe de normalisation de l'Electronic Industries Alliance (EIA) en matière de transistors.

Les SDRAM ont été conçues pour répondre à toutes les questions de performances bien qu'il soit apparu très vite qu'elles apportaient peu à la performance et causaient des difficultés de compatibilité. Les premiers circuits contenaient deux lignes d'horloge ce qui s'est avéré insuffisant. On a donc eu des types de modules à 2 et 4 lignes d'horloge. La carte mère doit être adaptée à l'un ou à l'autre. Le cadencement est en théorie 5-1-1-1 à 66MHz, mais beaucoup ne fonctionnent qu'à 6-2-2-2 quand ils marchent par paire avec les ponts i430VX, iS5571.

Les SDRAM sont qualifiées en MHz comme les bus.

La SDRAM simple n'est plus fabriquée depuis 1999.

Une SDRAM PC100 avec CAS=2, aura un délai initial de 9 cycles

pour le premier mot, les 3 mots suivants ne demandant que 3 cycles en tout.

La mémoire aura ainsi émis 32 octets en 12 cycles.

Elles diffèrent de la SDRAM par la capacité à

lire un bit aussi bien sur le front de montée que sur le front de

descente de l'horloge, ce qui double le débit potentiel soit 1 mot

chaque 5 ns. Leur fabrication a commencé en 1998.

Attention comme ailleurs, il ne s'agit pas du

temps d'accès.

JEDEC SDRAM est la variante normalisée. Comme les autres c'est un interface synchrone commandé par l'horloge. Il inclut aussi l'organisation en double banc et un mode par bouffées (burst mode) pour 1 bit, 2 bits, 4 bits, 8 bits et la page complète. L'interface contient un registre de mode modifiable qui détermine le mode par bouffées, le type séquentiel ou entrelacé, la longueur de la bouffée et la durée du CAS.

Schéma d'implantation d'une SDRAM

5.3 PC100 SDRAM

Intel a produit les circuits de commande du bus à 100 MHz et en même temps les spécifications de fabrication des circuits de mémoire pour fonctionner à cette fréquence avec le pont i440BX.

Dans le meilleur des cas, les circuits PC100 fonctionnent à 4-1-1-1.

On prendra garde au fait que les performances des SDRAM PC100 sont proches de celles du cache L2 toujours en débit mais pas en temps d'accès.

On a ici un circuit mixte. Les fabricants ont ajouté un peu de RAM statique (SRAM) dans le circuit dans une fonction de cache. Ramtron International Corporation fournit ces mémoires qui ne sont utilisées que dans des machines assez spéciales. Le débit devient celui du cache à 200 MHz dans le meilleur des cas. Les mémoires ESDRAM peuvent remplacer directement les SDRAM sous la réserve suivante :

Attention, il faut que le BIOS soit modifié pour bénéficier

de ces gains de temps et dans le cas défavorables, une petite pénalité

intervient pour charger la mémoire SRAM.

Le coût de la ESDRAM est de 4 fois celui des DRAM banales.

6. LES DRAM _À PROTOCOLE

Toutes les DRAM précédentes ont des lignes d'adresses de données et de commande séparées. C'est un facteur de limitation des performances. L'idée relativement nouvelle est de placer tous ces signaux sur un même bus. Il y a deux réalisations de ce type dites basées sur un protocole : Direct Rambus DRAM (DRDRAM) de la société Rambus et SyncLink DRAM ou SLDRAM

Une réalisation est proposée par la société américaine Rambus, sous le nom de DRDRAM. Fujitsu, Nec et Toshiba et Samsung produisent des puces de 71 et 144 Mbits. La technique d'accès est modifiée par l'intégration d'un bus propre de 8 ou 16 bits dans le banc de mémoire. La fréquence interne du système Rambus est de 533MHz. Il transmet une donnée chaque 3,75 ns, ce qui est quatre fois plus rapide que le débit usuel à 66MHz. La contrepartie est que tous les organes, processeur comme mémoire doivent être dotés du RAMbus. À son avantage, les débits sont de 1,6 Go/s avec l'espoir d'atteindre 2,4 Go/s. Toutefois le bus standard est étroit, malgré les performances intrinsèques, il n'apporte qu'un facteur 2 par rapport aux autres SDRAM sur 64 bits. Le RAMBUS est utilisé depuis 1998 par Silicon Graphics pour les stations de travail Indigo2, par Nintendo pour le jeu vidéo N64 3D, par Cirrus Logic pour les accélérateurs CL-GD5462, par Creative Labs pour la carte graphique Blaster 3D. Intel a créé le jeu de composants 820 dit CAMINO pour relier les RDRAM au Pentium III et renouvelait soccord avec Rambus pour 5 ans en septembre 2001. Et pourtant en février 2002, Intel annonçait que la mémoire Rambus ne serait plus utilisée dans les nouveaux produits, préférant la mémoire DDRDRAM, voir ci-dessous. ON TROUVERA L4HUSTOIRE DE LA SOVI2T2 RAMBUS et de son produit à http://www.xbitlabs.com/mainboards/rambus/.

Exemple d'implantations

C'est peut être la solution à long terme. Contrairement

au DRDRAM précédent, propriété de Rambus, c'est

une technique publique bien qu'issue de fabricants. L'organisation passe

de 4 bancs à 16 bancs simultanés avec une logique de commande

rénovée. Sa bande passante est 3,2 Go/s.

Sa fabrication a commencé en 1999.

7. DDRDRAM (double data rate DRAM) ou encore DDRAM

C'est une évolution de la SDRAM qui transfère les

données sur les deux fronts, montée et descente de l'horloge,

mais les adresses sont toujours transférées en mode normal.

| Type de barrette | Taille |

| Barrette SIMM (32 bits) EDO * | 16 Mo |

| Barrette SIMM (32 bits) EDO * | 32 Mo |

| Barrette DIMM (64 bits) SDRAM * PC-100 * | 32 Mo |

| Barrette DIMM (64 bits) SDRAM PC-100 * | 64 Mo |

| Barrette DIMM (64 bits) SDRAM PC-100 * | 128 Mo |

| Barrette DIMM (64 bits) SDRAM PC-100 * | 256 Mo |

| Barrette DIMM (64 bits) SDRAM PC-133 | 64 Mo |

| Barrette DIMM (64 bits) SDRAM PC-133 | 128 Mo |

| Barrette DIMM (64 bits) SDRAM PC-133 | 256 Mo |

| Barrette (64 bits) RDRAM | 128 Mo |

| Barrette (64 bits) DDR-SDRAM | 128 Mo |

| Barrette (64 bits) DDR-SDRAM | 256 Mo |

8. PRINCIPE DE FONCTIONNEMENT

DE LA SRAM

Un bit de SRAM est enregistré dans un montage à 6 transistors dont le schéma possible est donné ci-dessous.

Quelques données utiles :

| Technique de mémoire | Bus usuels fourchette en MHz | Au mieux |

| Cache L2 SRAM «burst pipeline» | 3-1-1-1 | |

| Cache L2 SRAM asynchrone | 3-2-2-2 | |

| Mémoire DRAM | 4,77 à 40 | 5-5-5-5 |

| Mémoire DRAM FPM | 16 à 66 | 5-3-3-3 |

| Mémoire DRAM EDO | 33 à 75 | 5-2-2-2 |

| Mémoire DRAM BEDO | 60 à 100 | 5-1-1-1 |

| Mémoire SDRAM | 60 à 100 | 5-1-1-1 |

9. UN TOUR PAR LES TECHNIQUES ANCIENNES

Les premières mémoires ont été faites avec des tubes à vide. C'était volumineux, peu fiable et consommateur de courant électrique. Avec quelques milliers de tubes on stockait 20 nombres dans l'ENIAC.

La première technique originale a été la ligne à retard à mercure, inventée au MIT pour des radars. Les signaux sont transformés en ondes sonores, envoyées dans un tuyau empli de mercure. Le son se propage dans la boucle qui contient ainsi plusieurs bits dans sa longueur. On a stocké un signal pendant quelques millisecondes. La sortie est bouclée sur l'entrée pour assurer la conservation d'un millier de bits.

La ligne à retard a été utilisée dans BINAC, EDVAC, UNIVAC. D'autres matériaux comme le quartz et le verre ont parfois remplacé le mercure..

Les tubes électrostatiques de Williams ont remplacé les lignes à retard dans les années 1960, concurremment avec les tambours magnétiques dans le Manchester Mark I en premier.

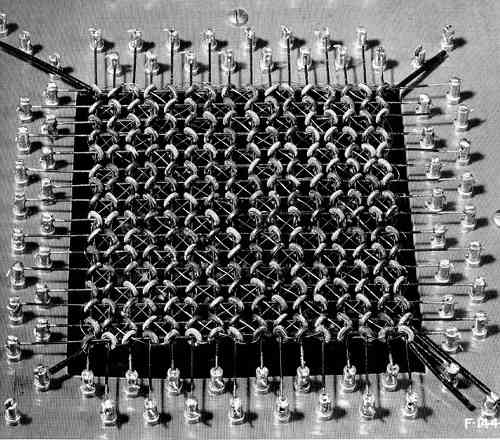

La

technique suivante fut celle des tores magnétiques de ferrite inventés

et brevetés en 1949 à l'occasion du projet Whirlwind. Elle

a duré jusqu'au début des années 1980. Le bit de mémoire

était porté par un anneau d'environ 0,25 mm de diamètre.

Cet anneau en ferrite pouvait prendre deux états magnétiques

commandables par un courant électrique. Les anneaux étaient

répartis en tableaux plats, chaque anneau traversé par trois

fils, deux d'écriture et un de lecture. Un fil d'écriture

était affecté à un rang horizontal, l'autre à

un rang vertical. Il suffisait de fournir à une colonne et à

une rangée la moitié de la puissance nécessaire à

l'écriture et seul l'anneau à l'intersection des deux fils

était écrit.

Principe des mémoires

à ferrite

Une vraie mémoire

La lecture se faisait

par écriture !

Après décodage

de l'adresse, la ligne et la colonne en cause recevaient un courant d'écriture,

écriture du 0 par exemple. Si le tore contenait 0, le fil de lecture

ne détectait rien, s'il contenait 1, le fil de lecture détectait

le changement d'état. La lecture était destructive, il fallait

récrire le point.

La mémoire à tores est permanente sans consommation. Le temps d'accès est de l'ordre de la microseconde. Sa fabrication en faisait un objet cher.

La technique suivante

est la DRAM, due aux fondateurs d'Intel, Robert Noyce et Gordon Moore.

Le premier circuit DRAM modèle 1103, avait une capacité de

1 kbits en 1971.